### Scopo della lezione

- Analizzare i tipi di "macchine"

- Indirizzamento e memorie

- Tipi di dato

- Little endian e big endian

- Indirizzamento logico e fisico

- Comprendere la struttura del micro

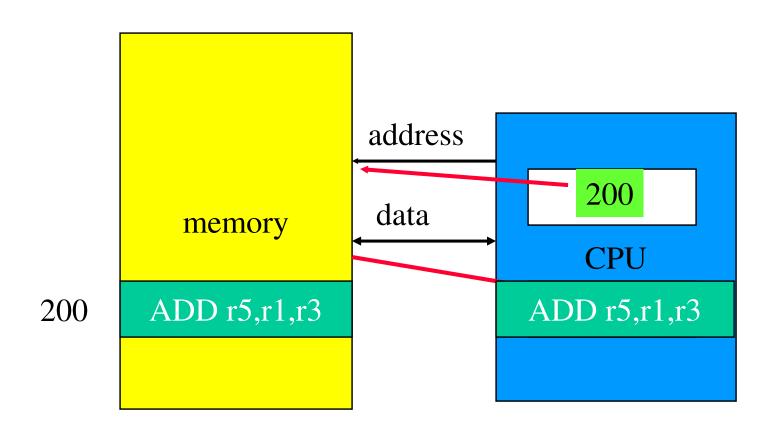

## Von Neumann architecture

- La memoria contiene dati e istruzioni.

- La CPU "fetcha" istruzioni dalla memoria e legge e scrive dati sempre sulla stessa.

- I registri della CPU lavorano per l'esecuzione del programma: program counter (PC), instruction register (IR), registri general-purpose, ecc.

## CPU + memoria comune

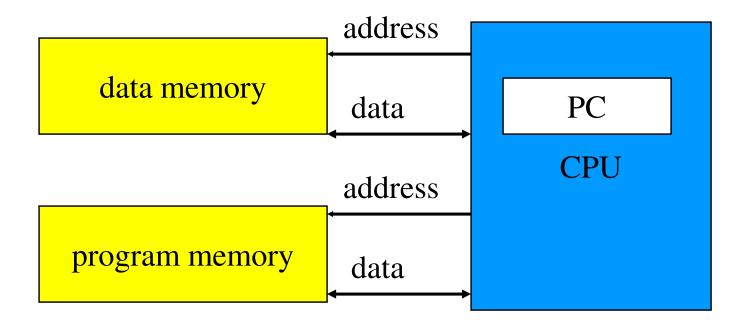

## Harvard architecture

Caratterizzata da memoria dati e di programma separate

## von Neumann vs. Harvard

- Harvard non può utilizzare codice che si auto-modifica, quindi è più sicura.

- Harvard permette 2 fetch alla memoria simultanei

- Molti DSP sono progettati secondo lo schema Harvard architecture a causa di necessità di data-streaming:

- maggiore memory bandwidth;

- Bandwidth maggiormente predicibile, a causa dello schema più rigido.

## RISC vs. CISC

- Complex instruction set computer (CISC):

- Permette molti modi di indirizzamento;

- Permette un più elevato numero di operazioni codificate.

- Reduced instruction set computer (RISC):

- Permette solamente le load/store di dati e le fetch di codice;

- Permette di utilizzare istruzioni in pipeline.

## Caratteristiche dell'Instruction set

- Lunghezza fissa (RISC) vs. lunghezza variabile (CISC).

- Modi di indirizzamento.

- Numero di operandi permessi per istruzione (ad esempio il motorola 698332 permette le tblu e tblun che sono operazioni di index/ratio su vettori che rendono index e ratio in una sola istruzione; come parametri hanno il puntatore al vettore e la grandezza su cui eseguire idx/ratio).

- Tipi di operandi.

### Implementazioni diverse dello stesso core

- Architetture ben riuscite presentano implementazioni diverse:

- Con diverse frequenza di clock;

- Diverse capacità (parallelismo) di bus;

- Diversi tagli di memoria e di cache (ove presente);

- etc.

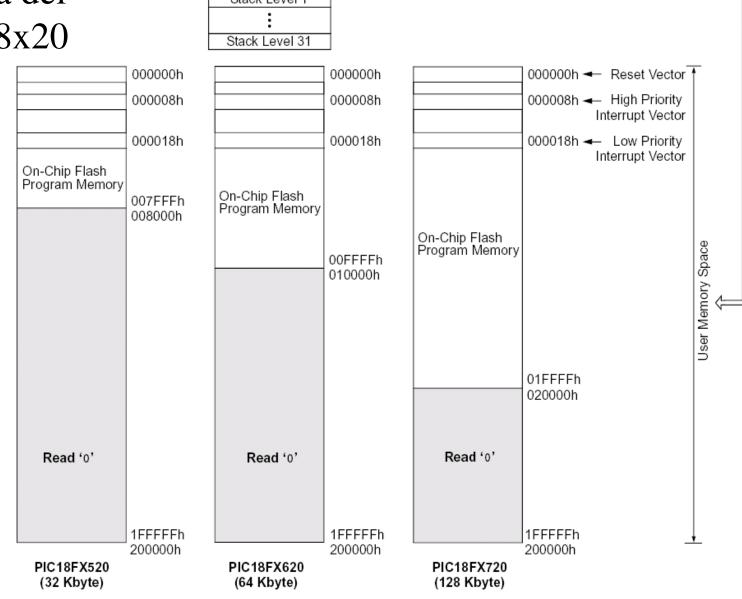

|            | Program Memory |                               | Data Memory     |                   |     | 10-bit      | ССР   | MSSP |                            |       | Timers       | Ext | Max           |

|------------|----------------|-------------------------------|-----------------|-------------------|-----|-------------|-------|------|----------------------------|-------|--------------|-----|---------------|

| Device     | Bytes          | # Single-Word<br>Instructions | SRAM<br>(bytes) | EEPROM<br>(bytes) | I/O | A/D<br>(ch) | (PWM) | SPI  | Master<br>I <sup>2</sup> C | USART | 8-bit/16-bit |     | Fosc<br>(MHz) |

| PIC18F6520 | 32K            | 16384                         | 2048            | 1024              | 52  | 12          | 5     | Υ    | Υ                          | 2     | 2/3          | N   | 40            |

| PIC18F6620 | 64K            | 32768                         | 3840            | 1024              | 52  | 12          | 5     | Υ    | Υ                          | 2     | 2/3          | N   | 25            |

| PIC18F6720 | 128K           | 65536                         | 3840            | 1024              | 52  | 12          | 5     | Υ    | Υ                          | 2     | 2/3          | N   | 25            |

| PIC18F8520 | 32K            | 16384                         | 2048            | 1024              | 68  | 16          | 5     | Υ    | Υ                          | 2     | 2/3          | Υ   | 40            |

| PIC18F8620 | 64K            | 32768                         | 3840            | 1024              | 68  | 16          | 5     | Υ    | Υ                          | 2     | 2/3          | Υ   | 25            |

| PIC18F8720 | 128K           | 65536                         | 3840            | 1024              | 68  | 16          | 5     | Υ    | Y                          | 2     | 2/3          | Υ   | 25            |

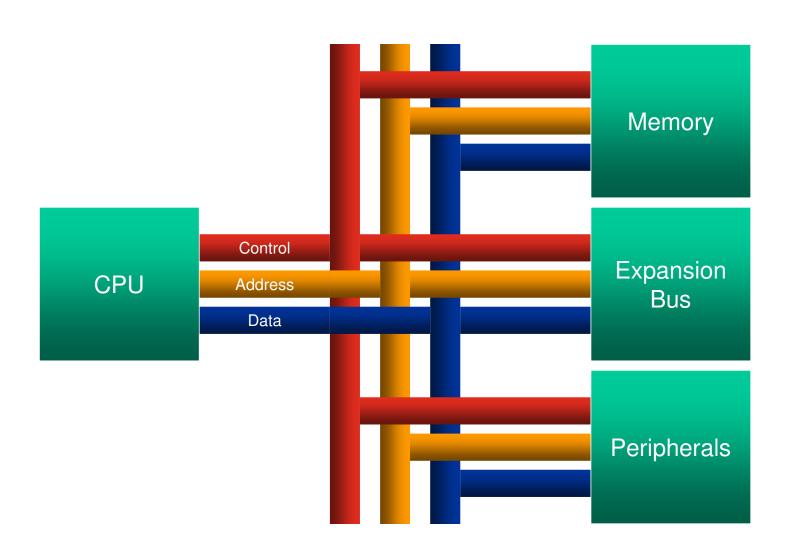

#### Struttura di un PC

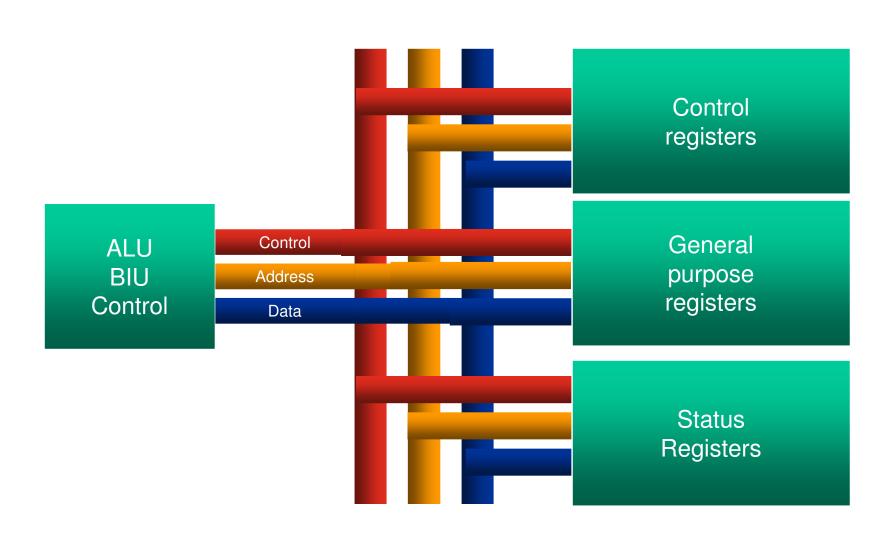

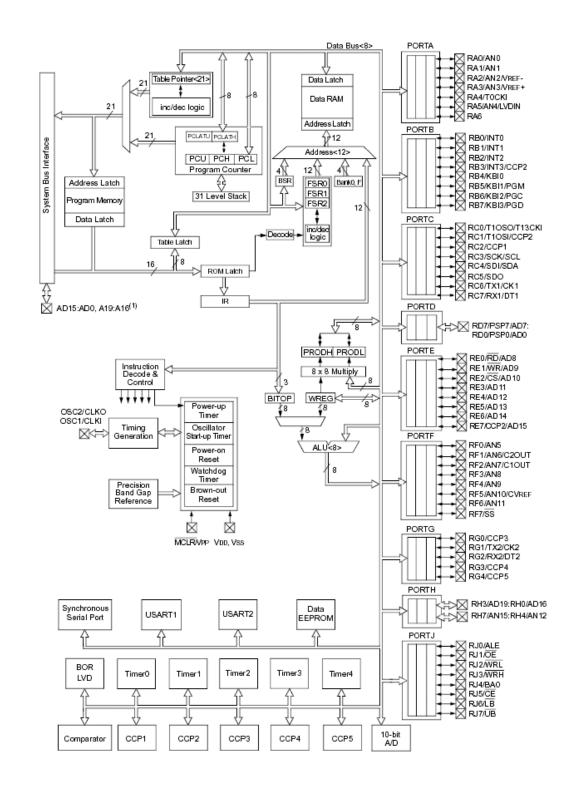

## Struttura di un microprocessore

## **Basics**

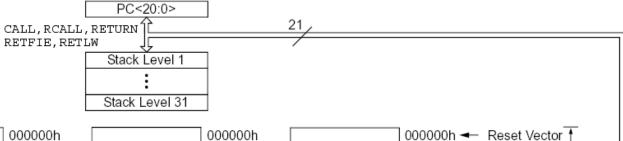

- La memoria dei PIC18F8x20 è byte-addressable

- Ogni volta che un indirizzo è emesso sull'address bus,

viene specificata una precisa locazione di memoria

- Il Byte è la "basic memory unit"

- Viene anche data la possibilità di leggere/scrivere più di un byte con una sola operazione, ovvero con un solo <u>ciclo di</u> <u>bus</u>

- 16-bit: word, 2 byte consecutivi

- 32-bit: doubleword, 4 byte consecutivi (questa operazione però non è possibile con i PIC, è invece possibile con gli ARM, I 68000 Motorola, I Pentium ecc...).

# Memoria Logica vs. Fisica

- La memoria logica è la "rappresentazione" della memoria vista dal programmatore

- Un grande byte-addressable array di byte

- Si possono leggere/scrivere byte, word o doubleword

- Non ci si preoccupa di come I dati o il programma è letto (fetched=andare a prendere) dalla memoria, si vede solo il risultato dell'accesso alla memoria a 1, 2, or 4 byte

- Memoria Fisica

- E' l'organizzazione fisica delle celle di memoria, che non è visibile al programmatore

- L'Unità di accesso alla memoria fisica è uguale alla larghezza del data bus.

- Ad esempio 16 bit in PIC18F8x20, 32 bit in 80386 e nel motorola 68000, 64 bit nel Pentium

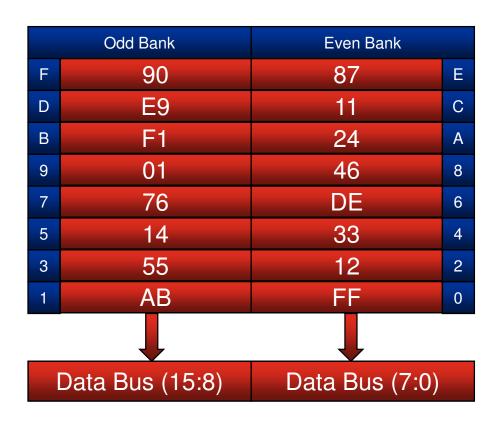

## PIC18F8x20 memoria fisica

- Una "read" al byte di address 0: rende=FF

- Una "read" a word dall'address 0: restituisce=ABFF

- Una "read" di una doubleword dall' address 0: restituisce=5512ABFF

# Ordine dei byte nel PIC18F8x20

- Le locazioni 0 and 1 contengono FF e AB...

- ma un accesso a word all'address 0 restituisce ABFF

- I PIC usano l'ordinamento di tipo "little endian" byte order

- L'indirizzo richiamato (0) punta al byte di peso inferiore del risultato:LSB

- Il byte di peso maggiore del risultato è preso dal byte di indirizzo sequenziale più alto nella memoria (1): MSB

# Byte ordering

- Little endian vs. big endian

- Nel caso opposto di codifica Big Endian, il byte di peso maggiore è letto nella locazione di indirizzo richiamata (0), mentre l'LSB è letto nell'indirizzo seguente (1)

- UNIX lavora in Big Endian, Motorola

- L'ordinamento dei Byte è una caratteristica della architettura.

## Allineamento dei Byte

|   | Odd Bank        | Even Bank      |  |  |  |  |

|---|-----------------|----------------|--|--|--|--|

| F | 90              | 87 E           |  |  |  |  |

| D | E9              | 11 C           |  |  |  |  |

| В | F1              | 24 A           |  |  |  |  |

| 9 | 01              | 46 8           |  |  |  |  |

| 7 | 76              | DE 6           |  |  |  |  |

| 5 | 14              | 33 4           |  |  |  |  |

| 3 | 55              | 12 2           |  |  |  |  |

| 1 | AB              | FF 0           |  |  |  |  |

|   |                 |                |  |  |  |  |

|   | Data Bus (15:8) | Data Bus (7:0) |  |  |  |  |

- Leggendo la word all'address 0 data:(15:8)=AB,data(7:0)=FF

- I dati sono passati al data bus nell'ordine corretto di peso dei bit (MSb a sx e LSb a dx)

- Questo è un accesso alla memoria allineato ai pesi dei bit.

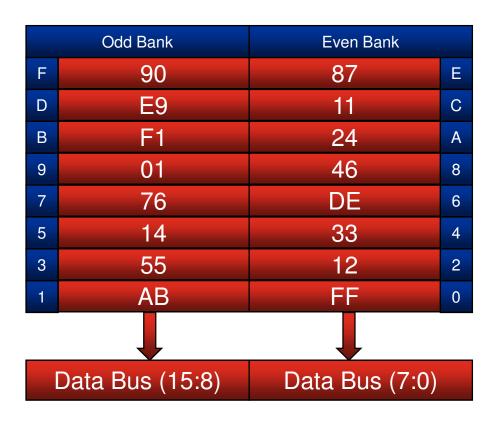

# Allineamento dei Byte

- Cosa accade se leggo una word all'address 1 ?

- È un accesso valido alla memoria, in linea di principio si può leggere anche a indirizzi dispari, ma quale è lo svantaggio???????

- Il risultato è 12AB

- Ma I byte nel data bus NON SONO ALLINEATI: data(15:8)=AB,data(7:0)=12

- E inoltre devi generare due indirizzi!!! Due accessi al bus

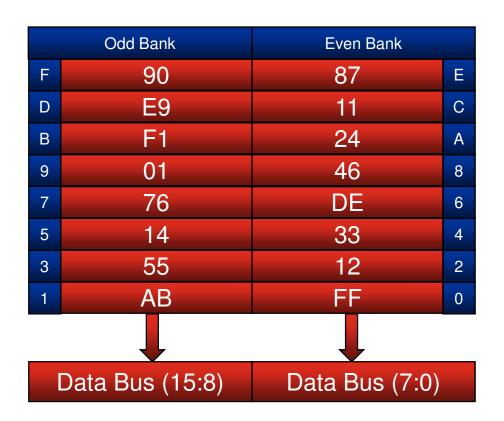

#### Allineamento dei Byte: Bad/Good habits

- Ogni volta in cui facciamo un accesso alla memoria leggendo più di un byte, i byte letti debbono essere allineati nel corretto ordine in accordo alla architettura

- Se leggiamo una word all'address 1, il byte all'address 2 deve essere memorizzato nell'MSB del data bus e il byte all'address 1 nell'LSB del data bus

- In alcuni micro si era costretti a farlo a mano, in molti micro ora si fa in automatico; nei micro che non sono protetti da questo punto di vista è meglio evitare accuratamente di impantanarsi in questo genere di problemi......

### Allineamento dei Byte: Bad/Good habits (2)

- Ci si deve preoccupare di accessi alla memoria non allineati al corretto ordine dei byte ?

- Si, se volete creare un programma che giri veloce e occupi il bus in modo efficiente!

- In accessi non allineati il processore deve:

- Leggere il byte ad indirizzo dispari (primo accesso alla memoria attraverso il bus)

- Leggere il byte ad indirizzo pari (secondo accesso alla memoria attraverso il bus)

- Allineare I due byte (overhead nell'hardware o nel software)

- In un accesso allineato invece il processore deve semplicemente:

- Leggere il byte pari (un accesso al bus), in automatico si riceve anche il byte dispari se si accede anche alla parte alta del bus dati.

- Accessi allineati sono almeno doppiamente veloci rispetto a quelli non allineati

## Tipi di dato

#### Numeri interi

- Bit, Nibble, Bytes, Words, Doublewords

- Signed/unsigned

#### Numeri in floating point

- Formati diversi dai numeri interi

#### Testo

- 7-bit ASCII char (lettere, caratteri)

- 8-bit codifica ASCII che permette ulteriori 128 simboli

- Stringhe: sequenze di char

- Array: sequenze of numeri, caratteri

#### Files

- Immagini (.jpg, .gif, .tiff,...)

- Video (MPEG, .avi, Quicktime,...)

- Audio (.wav, .mp3,...)

- Tutto è gestito come sequenza (array) di byte memorizzati

- Il data type dipende dalla modalità di accesso ai dati e dal modo di usarli

## Tipi di Dato

- 16 signed/unsigned 8-bit byte

- 8 signed/unsigned 16-bit word

- 4 signed/unsigned 32-bit doubleword

- Una stringa

- Istruzioni e operandi (se program memory)...

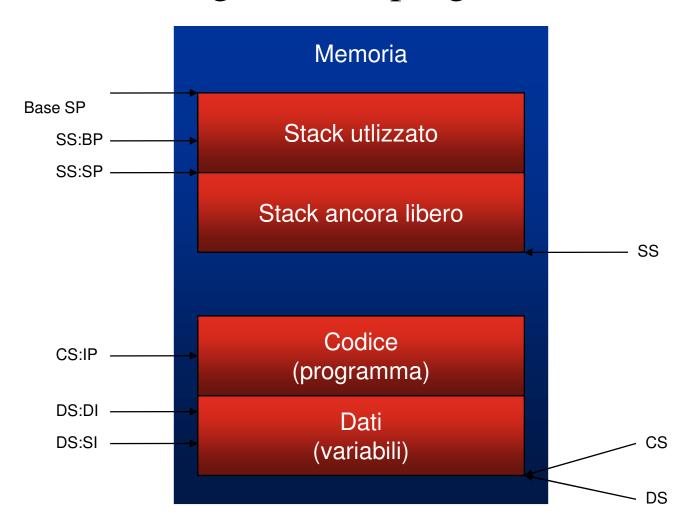

## Memoria segmentata

• Partizione logica di un programma

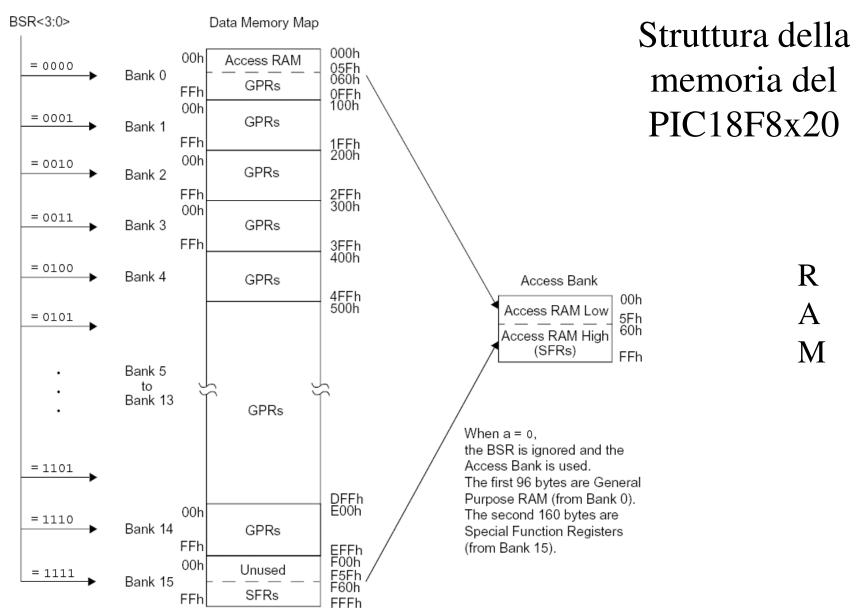

Struttura della memoria del PIC18F8x20

F H

When a = 1, the BSR is used to specify the RAM location that the instruction uses.